|

今日视点

本报驻韩国记者 薛严

韩国总统朴槿惠6月30日在中国西安参观了三星电子半导体工厂。该工厂建设第一期投资总额达70亿美元,是韩国公司在中国中西部投资规模最大的工厂,集中体现了三星电子在飞速发展的中国及全球半导体市场上先发制人的姿态。

说起半导体,上一代中国人会因为一个特定历史年代对收音机的普遍称呼而产生一定误会。但是,今天身处智能时代的我们真的有必要观察一下,我们邻国最大的电子企业在半导体,特别是闪存事业上取得的长足进步。因为当三星电子近日表示,从8月6日起在全球最先开始量产新概念3D垂直堆叠型结构NAND闪存芯片(3D V-NAND)的时候,业界有人惊呼,三星电子正在以独创技术突破半导体技术极限。

打破传统结构

完成制程创新

之所以说身处智能时代的我们应该更多地了解半导体事业的发展,是因为我们手里的平板电脑、智能手机以及一切使我们生活变得更便利的智能产品都离不开闪存的技术进步。特别是NAND闪存在断电情况下也能完整保存数据,所以主要用于在智能手机中存储音乐、照片和视频等,也可用于取代传统HDD硬盘的固态硬盘SSD中。而三星电子作为全球NAND闪存技术的领导者,正在掀起闪存事业的一场又一场革命。

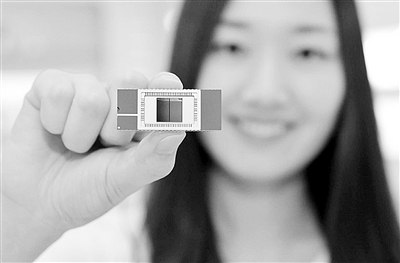

三星电子此次推出的3D垂直堆叠型结构NAND闪存芯片规格为128Gb,为业界最大容量。该产品同时采用了三星电子独创的“3D圆柱形电荷捕获型栅极存储单元结构技术”和“3D垂直堆叠制程技术”,与采用20纳米级单层结构的高性能NAND闪存产品相比,密度提高了两倍以上,由此显著提高了生产效率。

到目前为止,业界主要投入量产的闪存芯片采用的是40多年前开发的浮栅结构。传统NAND闪存由控制栅和浮栅组成,并在以导体制成的浮栅上存储电荷。当微细化发展到10纳米级以下时,存储单元之间的电极干扰将会加重,使得制程的微细化变得很困难。随着近来10纳米级制程工艺正式开始投入使用,存储单元间的间隔大幅缩小,使得电子外漏导致的电子干扰现象越来越严重。从某种程度上说,NAND闪存的微细化技术已达到了物理极限。

然而,三星电子此次将原来单层排列的存储单元以3D垂直堆叠方式重新排列,不仅同时实现了结构创新和制程创新,更将原有问题一并解决,使3D闪存芯片量产成为可能。

应用最新工艺

实现垂直堆叠

三星电子通过多年研究设计出的“3D圆柱形电荷捕获型栅极存储单元结构技术”,把存储单元像盖摩天大楼一样垂直堆叠24层,是三星电子在全球领先开发的2D平面电荷捕获型栅极芯片技术(2D CTF)的立体3D进化版。

CTF结构仅由控制栅组成,取代传统浮栅的是奶酪状的绝缘体,并在该绝缘体的空隙中存储电荷。由于只有一个栅极,存储单元的高度因而较低,而且绝缘体可以减少存储单元之间的干扰,相对更容易实现微细化。而三星电子新设计出的3D CTF结构将传统的单层CTF结构改良升级为3D立体结构。原来长方形的控制栅被改为像戒指一样中空的圆柱体,因而可以最大化的利用空间,并使堆叠制程更加容易实现。采用该结构的存储单元通过把电荷存储在具有高稳定性的绝缘体中,大幅减少了上下存储单元间的电子干扰现象。新产品的写入速度将提高两倍,作为存储单元寿命衡量标准的可擦写次数随产品种类不同也将提高两倍到十倍不等。

“3D垂直堆叠制程技术”是实现在尽可能小的芯片上放置尽可能多组件的技术。三星电子开发了从高层向低层穿孔以连接电极的蚀刻技术,以及将存储单元垂直围绕在各层板面上的门极结构技术等一系列独特并有突破性的工艺技术。

注重专利保护

倾力技术革新

三星电子在过去十年研究“3D垂直堆叠型结构NAND闪存”的过程中,研发了300余项核心专利,并已在韩国,美国和日本等世界各国提出了专利申请。由此,三星电子在事实上成功突破了10纳米级以下半导体技术的极限,为将来推出1Tb以上大容量NAND闪存确保了技术来源,也迈开了NAND闪存技术革新的脚步。换句话说,今后的技术竞争将不再是利用最新的光刻设备来追求微细化的竞争,而是迎来了加高堆叠层数来实现大容量化的彻底的技术转型。

美国市场调查机构预测,世界NAND闪存芯片市场将持续增长,从今年的236亿美元增长到2016年的308亿美元。三星电子在全球首次投入量产3D垂直堆叠型结构NAND闪存,确保了绝对的产品竞争优势,并将在今后以差别化的独创技术持续加强存储器芯片事业的竞争力。

(科技日报首尔8月8日电)

下一版

下一版